# A Digitally Controlled Low Voltage Variable Gain Amplifier with Constant Return Loss

Sotoudeh Hamedi-Hagh, Muhammad Yousuf Siddiqui, Mandeep Singh, and Shahab Ardalan

San Jose State University, Electrical Engineering Department, San Jose, CA 95192-0084

Abstract—This paper presents a Variable Gain Amplifier operating at 4GHz with 1.2V of supply voltage and 250MHz bandwidth. The proposed configuration uses a mixture of voltage and current mode techniques to achieve a constant return loss, at both the input and the output, giving efficient power transmission completely independent of gain variations. SPECTRE simulations on the designed amplifier reveal a -12dB to 15dB gain variation in 3dB steps, with both S11 and S22 staying constant with a mean of -16.83dB and -21.37dB respectively. SPECTRE simulations also show a 1dB Power Compression point of -18.15dBm at the highest gain and a Power Gain variation of -10.73 to 16.17dB. The amplifier is also stable for all gain variations and is designed using a 90nm CMOS processes.

*Index Terms*— CMOS, Noise Factor, Power Gain, Return Loss, RF Variable Gain Amplifier, VGA, Voltage Gain.

## I. INTRODUCTION

In wireless transmission, the signal strength between the transmitter and receiver depends upon many factors; the distance between the source and the receiver, condition of the channel and the path loss [1-3]. Therefore, the received signal is usually not constant, but rather varies depending on such factors. The Automatic Gain Control (AGC) block, deployed at the receiver end, plays an important role in ensuring that a constant amplitude signal is delivered to any subsequent stages for signal processing. Due to the rapid increase in the use of wireless communications systems, especially portable ones, the use of AGC blocks has consequently increased. The main part of the AGC block is the variable gain amplifier (VGA).

There are many different VGA topologies based on i) source degeneration [4], ii) transistor operating range variation [5], iii) current signal steering between the load and the supply voltage [6], iv) logarithmic gain control [7], v) gain control using a variable load [8] or vi) gain control using a variable linear resistor in the amplifier [9]. This paper describes a new simple VGA architecture, one which is based on a combination of current mode and voltage mode design to achieve constant return loss and good linearity while at the same time operating at a low voltage. Constant return loss ensures steady and efficient power transmission to and from

The authors are associated with the Department of Electrical Engineering at San Jose State University, One Washington Square, San Jose CA 95112-0084 USA, (email: hamedi@sjsu.edu)

the VGA.The VGA is designed to be used in a weaver receiver for WCDMA applications with 250MHz bandwidth. Section 2 describes the design of the amplifier and Section 3 provides the characteristics of the amplifier designed in a standard 90nm CMOS processes.

#### II. VGA DESIGN

## A. System Level Implementation

The system Level Implementation of the proposed architecture is shown in Fig. 1. In the first Stage, the input voltage signal is converted to a current signal with the aid of a voltage to current converter. In the second stage, that converted current signal is varied using a digitally controlled current mode block. Finally, in the third stage the processed current signal is changed back to voltage mode.

The main benefit of using such architecture is that the gain is varied at an intermediate stage, rendering the input and the output stages isolated from any impact of gain variations. This ensures that the input and output stage have a constant biasing level for all gain changes, hence giving a constant return loss ( $S_{11}$ ,  $S_{22}$ ) at any gain. This further implies that a single impedance matching network, at the input and the output, can be designed for the frequency band of interest.

## B. VGA Schematic

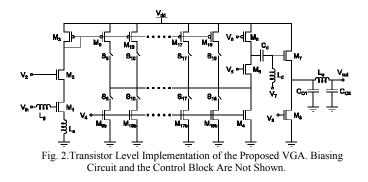

The complete transistor level diagram of the proposed VGA architecture is shown in Fig. 2.  $V_2$ ,  $V_4$ ,  $V_5$ ,  $V_6$ ,  $V_7$  and  $V_8$  are DC biasing voltages. These voltages are easily generated using an on chip constant  $g_m$  biasingcircuit.Measurement results in Section III indicate that using a constant  $g_m$  biasing circuit also minimizes the temperature and the process variations on the VGA operation. $L_g$  and  $L_s$  are used for the input impedance matching network; whereas  $C_{o1}$ ,  $C_{o2}$  and  $L_o$  make the output impedance matching network. An AGC circuit not shown controls all the switches.

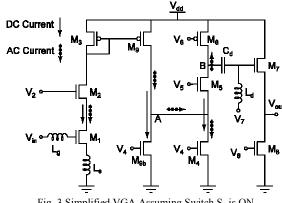

A simplified VGA circuit assuming one of the switches  $(S_9)$ is ON, is shown in Fig. 3. The DC and small signal AC currents in important branches are illustrated in the figure. The input signal is first converted to a current, by transistor M<sub>1</sub>, which flows into M<sub>3</sub> through M<sub>2</sub>. M<sub>2</sub> is required for better isolation.Transistor M<sub>3</sub> mirrors both the DC current and the small signal AC current to the other side. When switch  $S_9$  is ON and other switches are OFF, M<sub>9</sub> and M<sub>9b</sub> will be activated.  $M_{9b}$  is sized such that the entire DC current mirrored from  $M_3$ and flowing into M<sub>9</sub> goes through it. Similarly, M<sub>4</sub> acts as a constant current source and biases M5 and M6 with a constant DC current.

Moreover, the small signal AC current mirrored from M<sub>3</sub> to M<sub>9</sub> divides between transistors M<sub>9b</sub>, M<sub>4</sub> and M<sub>5</sub>.Transistor M<sub>5</sub> acts as a common gate amplifier, and converts the small signal AC current that flows through it into AC voltage at node B.Transistors M<sub>5</sub> and M<sub>6</sub> are biased with a fixed DC current using M<sub>4</sub>and therefore, the biasing voltages and small signal capacitors and resistorsassociated with node B remain constant. Finally, the AC voltage at node B is buffered to the output.

The ratio of  $M_9$ ,  $M_{10}$ ,  $M_{11}$ , ...,  $M_{17}$  and  $M_{18}$ , with respect to M3 is such that different AC currents are mirrored towards node A to achieve different gains. Switches S<sub>9</sub>, S<sub>10</sub>, S<sub>11</sub>, ...., S<sub>17</sub> and S<sub>18</sub> are used to turn ON and OFF a particular branch at a given time. Subsequently, the size of M<sub>9b</sub>, M<sub>10b</sub>, M<sub>11b</sub>,..., M<sub>17b</sub> and M<sub>18b</sub>transistors are selected to ensure the entire DC current from M<sub>9</sub>, M<sub>10</sub>,M<sub>11</sub>, ..., M<sub>17</sub> and M<sub>18</sub> flows through them, respectively. This guarantees that  $M_5$  and  $M_6$  are always biased with a constant current generated by M<sub>4</sub>.

The first branch in the circuit, composed of  $M_1$ ,  $M_2$  and  $M_3$ , and the finalbranch, consisting of  $M_4$ ,  $M_5$  and  $M_6$ , are driven with a constant DC current, generated by a gm biasing circuit, to minimize the impact of temperature variation on the circuit performance. Therefore, DC voltages at the input, node B and the output remain constant along with small-signal parasitic capacitors and resistors. This gives a near constant return losses at both the input and the output for different gain changes.

The number of switches and current steering branches control the gain steps. Whereas, the ratio of the transistors M<sub>9</sub>,  $M_{10}$ ,  $M_{11}$ , ...,  $M_{17}$  and  $M_{18}$  with respect to  $M_3$ , to a first order analysis, controls the gain at each step. Transistors are matched in the layout as much as possible to minimize the impact of process variation on the circuit performance.

Fig. 3.Simplified VGA Assuming Switch S<sub>9</sub> is ON

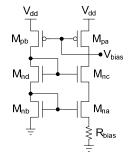

The circuit, shown in Fig. 4, is used to generate biasing voltagesin the VGA. The circuit uses positive feedback and ensures the input and the output biasing currents only depend on the ratio of transistor sizes. Since process and temperature variations affect both transistors equally while their ratio remains the same, desired biasing currents can be generated.

Fig. 4. The Constant gm Biasing Circuit

## C. Design Equations

The input of the VGA is a common source amplifier with inductive source degeneration to help with matching the real part of the impedance seen at the gate of M<sub>1</sub>to the input port impedance of  $50\Omega$ . The gate inductor, Lg, is used to cancel the imaginary component of the impedance at the gate of M<sub>1</sub>. The impedance matching network can approximately be designed using equations 1 and 2 [10]. Since it is difficult to achieve low noise figure as well as good impedance matching simultaneously, transistor M<sub>1</sub> width was optimized, such that to obtain reasonable values of both the noise figure as well as input matching.

$$Z_{in} \approx \frac{g_{m1}}{c_{gs1}} \times L_s(1)$$

$$\omega_o = \frac{1}{\sqrt{(L_g + L_s)c_{gs1}}}(2)$$

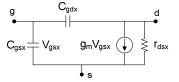

The gain of the device can be calculated using the following equations and the simplified small signal model shown in Fig. 5. The transconductance of the input stage, consisting of  $M_1$ and Ls, can be computed using

$$G_m = \frac{g_{m1}}{\omega_o c_{gs1}(R_s + \omega_T L_s)} \tag{3}$$

The small signal AC currentis given by

$$I_{AC} = G_m \times V_{in}(4)$$

Assuming  $M_2$  acts as a unity current buffer, the AC current in equation 4 is mirrored by the PMOS transistor  $M_3$  to the current steering branch which is switched ON. This current is multiplied by the corresponding mirror ratio as shown in equation 5.

$$I_{mirror} = I_{AC} \times \frac{N}{W}$$

(5)

where W is the channel width of transistor  $M_3$  and Nis the corresponding size of the mirror transistor  $M_9$ ,  $M_{10}$ ,  $M_{11}$ , ...,  $M_{17}$  and  $M_{18}$ that is switched ON.

This mirrored AC current divides between the impedance seen down into node A,  $Z_{DA}$ , and the impedance seen at the source of  $M_5$ ,  $Z_{UA}$ , shown in equation 6.

$$I_b = I_{mirror} \frac{Z_{DA}}{Z_{UA} + Z_{DA}} \tag{6}$$

where,

$$Z_{DA} \approx R_{DS4} ||\frac{1}{sC_{dg4}}||R_{DS9,\dots,DS18}||\frac{1}{sC_{dg9,\dots,dg18}}||\frac{1}{sC_{gs5}}(7)$$

$$Z_{UA} \approx \frac{1}{g_{m5}}(8)$$

At node B the small signal AC gain can be calculated using equation 9.

$$V_b = I_b \times Z_b(9)$$

where,

$$Z_b = (Z_6 || Z_5 || Z_{in7})(10)$$

The impedance seen at the gate of  $M_7$ , after neglecting the effects of  $C_{gd7}$  and  $C_{gd8}$ , is given by

$$Z_{in7} \approx (R_{ds8} || R_{ds7}) \left( 1 + \frac{g_{m7}}{sC_{gs7}} + \frac{1}{sC_{gs7}(R_{ds8} || R_{ds7})} \right) (11)$$

$$Z_5 \approx (g_{m5} Z_{DA} R_{ds5}) || \frac{1}{sC_{dg5}} (12)$$

$$Z_6 \approx R_{ds6} || \frac{1}{sC_{qg6}} (13)$$

where,  $Z_5$  and  $Z_6$  are the impedances seen looking into the drain of  $M_5$  and  $M_6$ , respectively.

Finally, the total gain at the output node in Fig. 3, combining the gain at node B with that of the buffer composed of  $M_7$  and  $M_8$ , is given by

$$\frac{V_{out}}{V_{in}} \approx \frac{I_b Z_b (g_{m7} + sC_{gs7})}{s(C_{gd8} + C_{gs7}) + g_{m7}}$$

(14)

These equations are used to calculate the voltage gain approximately and extract W and N. The output impedance matching is also achieved using a pi- network composed of  $L_o$ ,  $C_{o1}$ , and  $C_{o2}$ .

Fig. 5. Simplified Transistor Model Used for Small Signal Analysis

### III. MEASUREMENT RESULTS

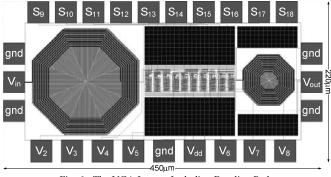

The VGA is designed using a 1.2V standard 90nm CMOS technology with 9 level of metallization. Only 3 metal layers are used for interconnects. Inductors are designed using top metal layer. The VGA is designed to match to  $50\Omega$  loads at input and output ports. All components are on-chip except  $L_d$ and C<sub>d</sub> which are used for biasing and coupling, respectively. The layout of the VGA is shown in Fig. 6 and includes inductors  $L_gand L_o$ , capacitors  $C_{o1}and C_{o2}$  and Transistors used in the VGA. The source degeneration inductor L<sub>s</sub> is small and is implemented using a wire inductor. Theoverall size of the layout including pads is 450µm by 220µm. The 10 gainstages are placed at the center of the design and occupy 120µm by 32µm of area. All designed inductors have patternground shield to maximize Quality Factor and minimize substrate losses. The achievedQuality Factorfor inductors, characterized by ADS momentum, is about 20. Pin V<sub>3</sub> is used to connect the external resistor to the constant g<sub>m</sub> biasing circuit.

Fig. 6. The VGA Layout Including Bonding Pads

#### A. S-Parameter Responses

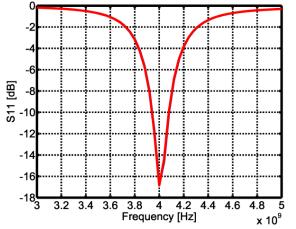

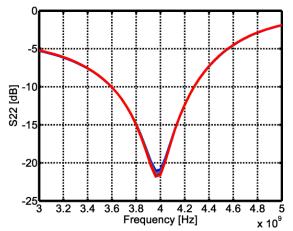

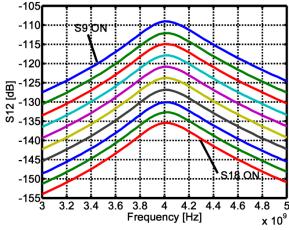

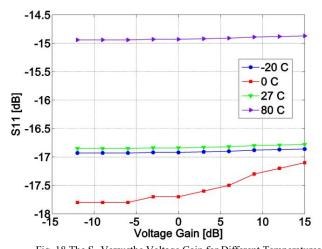

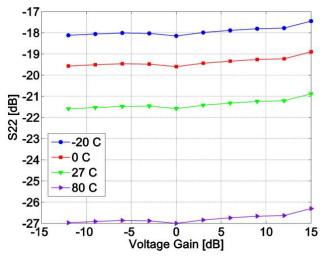

The S parameter responses of the circuit are shown in Figs.7, 8 and9. As seen in Fig.7,  $S_{11}$  or the input return loss remains relatively constant, with a mean of -16.83dB and very small - 0.3% to +0.12% variations for all process corners. The output return loss,  $S_{22}$ , is shown in Fig.8.  $S_{22}$  has a maximum variation of -2.3% to +1.03% from a mean of -21.37dB. Fig.9 shows  $S_{12}$  or the reverse isolation from the output to the

inputof the amplifier. The VGA considerably prevents reverse transmission, as seen in Fig. 9.

Fig. 7.The Input Return Loss (S<sub>11</sub>) as a Function of Frequency. The input return loss always remains low at -16.83dB at 4GHz because of the constant biasing current at input stage.

Fig. 8.The Output Return Loss (S<sub>22</sub>) as a Function of Frequency.The output return loss always remains low at -21.37dB at 4GHz because of the constant biasing current at output stage.

Fig. 9.The Reverse Isolation (S12) as a Function of Frequency

# B. Voltage Gain and Power Gain

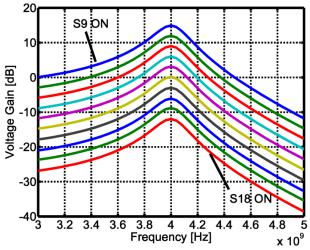

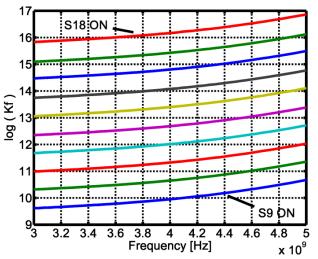

The variation of the voltage gain as a function of frequency is shown in Fig.10. The gain varies from 15dB (when  $S_9$  is ON) to -12dB (when  $S_{18}$  is ON) in 3dB steps with a center frequency of 4GHz. A constant bandwidth of 250MHz is maintained over the entire gain variation.

Fig. 10.The Voltage Gain in dB as a Function of Frequency. The gain varies from -12 to 15dB in 3dB steps for a 250MHz bandwidth centered at 4GHz.

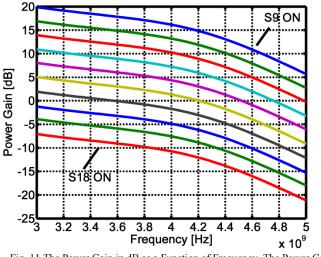

The VGA power gain is shown in Fig.11 as a function of frequency. The maximum power gain is 16.17dB(when S<sub>9</sub> is ON) and the minimum power gain is -10.73dB (when S<sub>18</sub> is ON).The VGA dissipates 5mW of power at the highest gain while tonly dissipates 3.8mW at the lowest gain.

Fig. 11.The Power Gain in dB as a Function of Frequency. The Power Gain Remains Constant Across a 250MHz bandwidth at 4GHz.

# C. Noise Figure

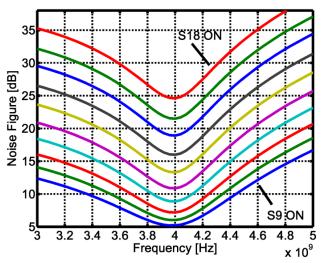

The Noise Figure of the VGA is shown in Fig. 12. The minimum noise figure, achieved at a voltage gain of 15dB, is

5.21dB, whereas the highest noise figure, achieved at a voltage gain of -12dB, is 24.6dB. Most noise contributions come from the resistive loss associated with the non-ideal inductors used in the design, especially  $L_g$ .

Fig. 12. The Overall Noise Figure as a Function of Frequency. Noise Figure Changes From 5.21dB to 24.6dB for Voltage Gains from 15dB to -12dB.

## D. 1<sub>db</sub> Power Compression Point

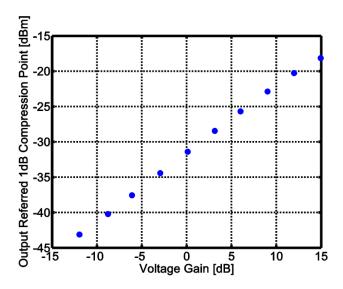

The output referred  $1_{dB}$  Power Compression point as a function of gain is represented in Fig. 13. A maximum and minimum Compression point of -18.18dBm and -43dBm is achieved respectively. The figure shows that as the voltage gain of the VGA is decreased the power gain also decreases, indicating that the VGA reaches its saturation power level earlier, hence having a low output referred compression point at lower gains.

Fig. 13.The Output Referred 1<sub>dB</sub> Power Compression Point as a Function of Voltage Gain at 4GHz Frequency.

## E. Stability

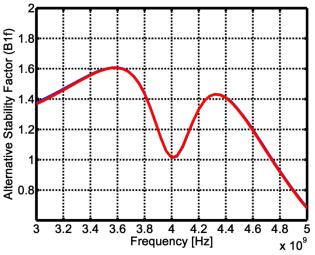

The stability of the VGA can be evaluated by considering the i) Stern Stability Factor  $K_f$  and ii)  $B_{1f} = s_{11} s_{22} - s_{12} s_{21}[11$ and 12]. The plots for the log(K<sub>f</sub>) and B<sub>1f</sub>, for different value of gains, are illustrated in Figs. 14 and 15, respectively. Log(K<sub>f</sub>) is used instead of regular K<sub>f</sub>, because the data were widely spread and a semi log plot better depicts the results. As shown in the graphs,  $K_f > 1$  or Log(K<sub>f</sub>)>0 and  $B_{1f} > 0$  for all gains, indicating that the VGA is always stable.

Fig. 14. The Stern Stability Factor, Log(Kf), as a Function of Frequency.

Fig. 15. The B<sub>1f</sub>Plot as a Function of Frequency for Different Values of Gain. The B1f Remains Greater than 0 Around the Bandwidth of Interest at 4GHz for all Gain Variations.

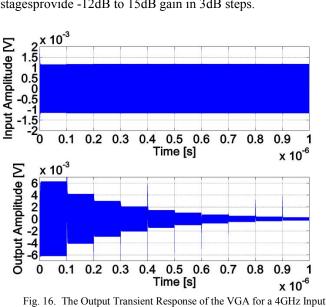

# F. Transient Analysis

To simulate the behavior of the VGA as a function of time, control signals were applied toswitches  $S_9$ ,  $S_{10}$ ,  $S_{11}$ , ...,  $S_{17}$  and  $S_{18}$  in order to turn a particular stage ON while other current steering stages are turned OFF for a given duration of

time. A sine wave is applied at the input and the corresponding output amplitudeof the VGA verses time, is shown in Fig.16. As can be seen from the figure, different stagesprovide -12dB to 15dB gain in 3dB steps.

Fig. 16. The Output Transient Response of the VGA for a 4GHz Inpu Sine Wave

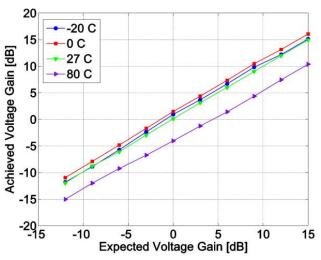

## G. Temperature and Processes Variations

Processes variations are minimized by using matched layout techniques and the use of dummy transistors. The temperature of the circuit was swept from -20°C to 80°C. The achieved voltage gain verses the expected voltage gain for different values of temperature is shown in Fig. 17. This figure indicates that the maximum positivegain error occurs at 0°C forall gain stages while the maximumnegative gain error occurs at80°C for all gain stages. There is approximately 5dB difference between the maximum positive gain error and the maximum negative gain for different values of temperature are shown in Fig. 18 and 19.

Fig. 17.The Achieved Voltage Gain Verses the Expected Voltage Gain for Different Temperatures

Fig. 18. The S11 Versus the Voltage Gain for Different Temperatures

Fig. 19.The S<sub>22</sub> versus the Voltage Gain for Different Temperatures

The complete VGA characteristics with transistor sizes are summarized in Table 1. The voltage gain of the VGA varies from -12dB to 15dB in 3dB steps with relatively constant input and output return losses of -16.83dB and -21.37dB, respectively. The VGA has a 1dB Power Compression point of -18.15dBm at a voltage gain of 15dB. The overall noise figure of the VGA varies from 5.21dB to 24.6dB while its Power Gain changes from -10.73dB to 16.17dB.

A comparison of the VGA, proposed in this work, compared with other previously reported designs is listed in Table 2. Our results are based on postlayout simulations including all parasitics. The Figure of Merit (FOM) referenced in Table 2 isdefined as

$$FOM = Log\left(\frac{DR \times BW}{|\Delta S_{11}| \times P_{dp} \times NF}\right)$$

(15)

where, DR is the dynamic range equivalent to the difference between maximum gain andthe minimum gain, BW is the bandwidth,  $\Delta S_{11}$  is the maximum change in  $S_{11}$ ,  $P_{dp}$  is the power dissipation and NF is the minimum Noise Figure. Compared with other designs, our architectureyields a near to constant return loss at both input and output.

| Switel<br>ON    | PMOS<br>Transistor<br>Widths (µm)* | NMOS<br>Transistor<br>Widths (µm)* | S <sub>11</sub><br>(dB) | S22<br>(dB) | Target<br>Voltage<br>Gain (dB) | Achieved<br>Voltage Gain<br>(dB) | Voltage<br>Gain Error<br>(dB) | Power<br>Gain<br>(dB) | Noise<br>Figure<br>(dB) |

|-----------------|------------------------------------|------------------------------------|-------------------------|-------------|--------------------------------|----------------------------------|-------------------------------|-----------------------|-------------------------|

| S <sub>9</sub>  | 43.20 (Mp)                         | 8,76 (M <sub>9b</sub> )            | -16.78                  | -20.88      | 15                             | 14.95                            | -0.05                         | 16.17                 | 5.21                    |

| S <sub>10</sub> | 25.68(M <sub>10</sub> )            | 5.04 (M <sub>10b</sub> )           | -16.79                  | -21.21      | 12                             | 11.98                            | -0.02                         | 13.21                 | 6.04                    |

| S11             | 17.40(M <sub>11</sub> )            | 3.48 (M <sub>11b</sub> )           | -16.8                   | -21.24      | 9                              | 9.02                             | +0.02                         | 10.25                 | 7.20                    |

| S12             | $11.64(M_{12})$                    | 2.40 (M <sub>12b</sub> )           | -16.82                  | -21.32      | 6                              | 6.01                             | +0.01                         | 7.24                  | 8.87                    |

| S <sub>13</sub> | $8.04(M_{13})$                     | 1.56(M <sub>13b</sub> )            | -16.83                  | -21.42      | 3                              | 3.14                             | +0.14                         | 4.36                  | 10.88                   |

| S14             | $5.52(M_{14})$                     | 1.08 (M <sub>14b</sub> )           | -16.84                  | -21.58      | 0                              | 0.12                             | +0.12                         | 1.34                  | 13.32                   |

| S15             | $3.84(M_{15})$                     | 0.84 (M <sub>15b</sub> )           | - 16.84                 | -21.46      | -3                             | -2.94                            | +0.06                         | -1.71                 | 15.99                   |

| S <sub>16</sub> | 2,64(M <sub>16</sub> )             | 0.60 (M <sub>16b</sub> )           | -16.85                  | -21.48      | -6                             | -6.09                            | -0.09                         | -4.86                 | 18.92                   |

| S17             | $1.92(M_{17})$                     | 0.36 (M <sub>17b</sub> )           | -16.85                  | -21.53      | -9                             | -8.77                            | +0.23                         | -7.54                 | 21.49                   |

| S <sub>18</sub> | $1.32(M_{18})$                     | 0.12 (M <sub>18b</sub> )           | - 16.85                 | -21.59      | -12                            | - 11.95                          | +0.05                         | - 10.73               | 24.6                    |

|                 |                                    |                                    |                         |             |                                |                                  |                               |                       |                         |

Table 1. Detailed Characteristics of the VGA

\*All transistor Lengths are 100nm.

Table 2. The Comparison of the VGA with Previous Works

| Ref.                    | [6]                            | [13]                        | [14]                 | [15]                     | [16]             | [17]                 | [18]              | This<br>Work        |

|-------------------------|--------------------------------|-----------------------------|----------------------|--------------------------|------------------|----------------------|-------------------|---------------------|

| Technology              | 0.18µm<br>CMOS                 | 0.18µm<br>CMOS              | 0.18µm<br>CMOS       | 0.18µm<br>CMOS           | 0.25µm<br>BiCMOS | 0.18µm<br>CMOS       | GaAs<br>HBT       | 0.09μm<br>CMOS      |

| Freq. (GHz)             | 2.4                            | 5.78                        | -                    | -                        | -                | -                    | -                 | 4                   |

| BW (MHz)                | 41                             | 1000 (MP)                   | 470 to 870           | 54 to 880                | 900              | 50 to 860            | 1500              | 250                 |

| V <sub>dd</sub> (V)     | 1.5                            | 1                           | 1.8                  | 1.8                      | 2.8              | 1.8                  | 7                 | 1.2                 |

| Gain<br>Variation       | 18.37 (HGM)<br>6.4 (LGM)       | 10.11 (HGM)<br>1.6 (LGM)    | 16dB to<br>- 17dB    | 15.5 (HGM)<br>- 5 (LGM)  | 28.2 to<br>-21.8 | 30dB                 | 10dB to<br>35.6dB | 15dB to<br>- 12dB   |

| S <sub>11</sub> (dB)    | - 12.01 (HGM)<br>- 19 (LGM)    | - 10.69 (HGM)<br>- 15 (LGM) | - 11 to<br>- 26 (MP) | - 18 (MGM)<br>- 32 (HGM) | -15 to-34        | -7 to-16             | - 5 to-7.5        | - 16.83             |

| 4S11 (dB)               | 6.99                           | 4.31                        | 15                   | 14                       | 19               | 9                    | 2.5               | 0.07                |

| S22 (dB)                | - 10.53 (HGM)<br>- 15.05 (LGM) | -                           | _                    | -                        | -9 to-26         | -11 to -16           | -5 to-20          | -21.37              |

| AS <sub>22</sub>   (dB) | 4.52                           | -                           | -                    | -                        | 17               | 5                    | 15                | 0.71                |

| NF (dB)                 | 2.15 (HGM)<br>3.97 (LGM)       | 1.94 (HGM)<br>3.96 (LGM)    | 4.3dB to<br>35dB     | 3.6 (HGM)<br>12.2 (LGM)  |                  | 2.5 to 3.5<br>withNC | 2dB to<br>11dB    | 5.21dB to<br>24.6dB |

| P <sub>1dB</sub> (dBm)  | - 11.22 (HGM)<br>- 9(LGM)      | - 16 (HGM)<br>- 14.5(LGM)   | _                    | -                        | 8.7<br>Max Gain  | -                    | -                 | - 18.18 to<br>-43   |

| P <sub>dp</sub> (mW)    | 6.45                           | 6.4                         | 21,96                | 50.4                     | 84               | 19.8                 | 278.6             | 3.8 to 5            |

| FOM                     | 2.25                           | 2.20                        | 0.00                 | 5.01                     | 16 71            | 14.44                | 5.00              | 22.12               |

FOM

2.35

3.20

8.89

5.21

15.71

14.44

5.82

23.13

HGM: High Gain Mode, LGM: Low Gain Mode, MP: Measured from Plot, FOM: Figure of Merit

FOM: Figure of Merit

FOM: Figure of Merit

#### IV. CONCLUSION

This paper presented a novel Variable Gain Amplifier operating at a central frequency of 4GHz with a bandwidth of 250MHz designed in a 90nm CMOS process. The voltage gain of the VGA varies from -12dB to 15dBin 3dB steps. This configuration provides a constant input return loss of -16.83dB and a constant output return loss -21.37dB when gain is varied. The VGA has a 1dB Power Compression point of -18.15dBm at a voltage gain of 15dB. The overall noise figure of the VGA varies from 5.21dB to 24.6dB while its Power Gain changes from -10.73dB to 16.17dB. The design has a very reliable performanceand can be fully integrated forhigh frequency automatic gain control applications.

## REFERENCES

- [1] W. Yanjie,B. Afshar, Y. Lu, V.C.Gaudet, A.M.Niknejad, "Design of a Low Power, Inductorless Wideband Variable-Gain Amplifier for High-Speed Receiver Systems," *IEEE Transactions on Circuits and Systems I*, Vol. 59, pp. 696-707, 2012.

- [2] Z. Chen, Y. Zheng, F.C. Choong, M. Je, "A Low-Power Variable-Gain Amplifier With Improved Linearity: Analysis and Design," *IEEE Transactions on Circuits and Systems I*, Vol. 59, pp. 2176-2185, 2012.

[3] K.T. Herring, J.W. Holloway, D.H. Staelin and D.W. Bliss, "Path-Loss Characteristics of Urban Wireless Channels," *IEEE Transactions* on Antennas and Propagation, Vol. 58, pp. 171-177, 2010. [4] J.J.F.Rijns, "CMOS low-distortion high-frequency variable-gain amplifier," *IEEE Journal ofSolid-State Circuits*, Vol.31, pp.1029-1034, 1996.

[5] S.Y. Kang, J. Jang, I.-Y. Oh and C.S. Park, "A 2.16 mW Low Power Digitally-Controlled Variable Gain Amplifier,"*IEEE Microwave and Wireless Components Letters*, Vol. 20, pp. 172-174, 2010.

[6] S.K.Alam, "A Novel 2.4 GHz CMOS Variable Gain Low Noise Amplifier Design for Bluetooth and Wireless LAN Applications," *International Conference onConsumer Electronics, Digest of Technical Papers*, pp.1-2, 2007.

[7] Z. Li, F. Guo, D. Cheng, H. Li and Z. Wang, "A Wideband CMOS Variable Gain Amplifier with a Novel Linear-in-dB Gain Control Structure," *IEEE International Workshop onRadio Frequency Integration Technology*, pp. 337-340, 2007.

[8] P.C. Huang, L.Y. Chiou and C.K. Wang, "A 3.3-V CMOS wideband exponential control variable-gain-amplifier," *IEEE International Symposium on Circuits and Systems, Proceedings*, Vol. 1, pp. 285-288, 1998.

[9] P.Naktongkul and A. Thanachayanont, "1.5-V 900-μW 40-dB CMOS variable gain amplifier," *IEEE International Symposium onCircuits and Systems, Proceedings*, pp. 1551-1554, 2006.

[10] T.K.K Tsang and M.N. El-Gamal, "Gain controllable very low voltage 8-9 GHz integrated CMOS LNAs,"*Radio Frequency Integrated Circuits (RFIC) Symposium*, pp.205-208, 2002.

[11] A.P. Stern, "Stability and Power Gain of Tuned Transistor Amplifiers," Proceedings of the IRE, Vol. 45, pp. 335-343, 1957.

[12] G. Gonzalez, "*Microwave Transistor Amplifiers: Analysis and Design*", Prentice Hall, 1984.

[13] S.K.Alam and J. DeGroat, "A 1-V 5 GHz Variable Gain Low Noise Amplifier in 0.18-µm CMOS,"*Canadian Conference onElectrical and Computer Engineering*, pp.576-579, 2006.

[14] J. Xiao, I.Mehr, and J. Silva-Martinez, "A High Dynamic Range CMOS Variable Gain Amplifier for Mobile DTV Tuner,"*IEEE Journal of Solid-State Circuits*, Vol.42, pp.292-301, 2007.

[15] D.-G. Im, S.-S. Song, H.-T. Kim and K. Lee, "A Wide-Band CMOS Variable-Gain Low Noise Amplifier for Multi-Standard Terrestrial and Cable TV Tuner,"*IEEERadio Frequency Integrated Circuits Symposium*, pp. 621-624, 2007.

[16] D.Coffing, E. Main, M. Randol and G. Szklarz, "A variable gain amplifier with 50-dB control range for 900-MHz applications,"*IEEE Journal of Solid-State Circuits*, Vol. 37, pp. 1169-1175, 2002.

[17] K.S. Chen, N.T.Hsu, K.C.Lu, T.S.Horng and J.M. Wu, "A variable gain low-noise amplifier with noise and nonlinearity cancellation for DVB applications,"*Asia Pacific Microwave Conference*, pp. 1144-1147, 2009.

[18] K.W.Kobayashi, A.K.Oki, L. Tran and D.C.Streit, "A novel baseband-1.5 GHz monolithic HBT variable gain amplifier with PIN diode gain control,"*IEEE Microwave and Millimeter-Wave Monolithic Circuits Symposium, Digest of Papers*, pp.181-184, 1995.